## EE 330 Lecture 34

**Layout of Current Mirrors**

Common-Centroid Layouts

High Gain Amplifiers

Cascode Amplifiers

## Fall 2024 Exam Schedule

Exam 1 Friday Sept 27

Exam 2 Friday October 25

Exam 3 Friday Nov 22

Final Exam Monday Dec 16 12:00 - 2:00 PM

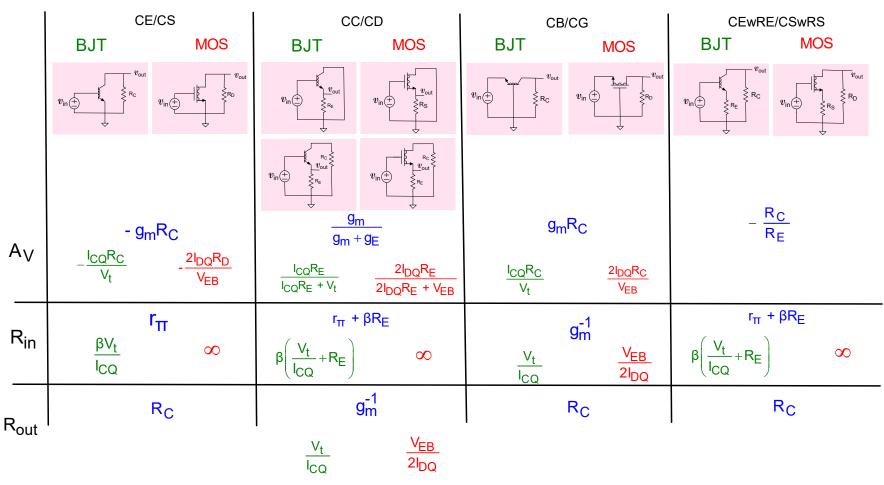

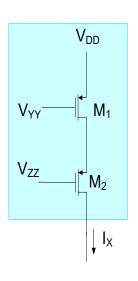

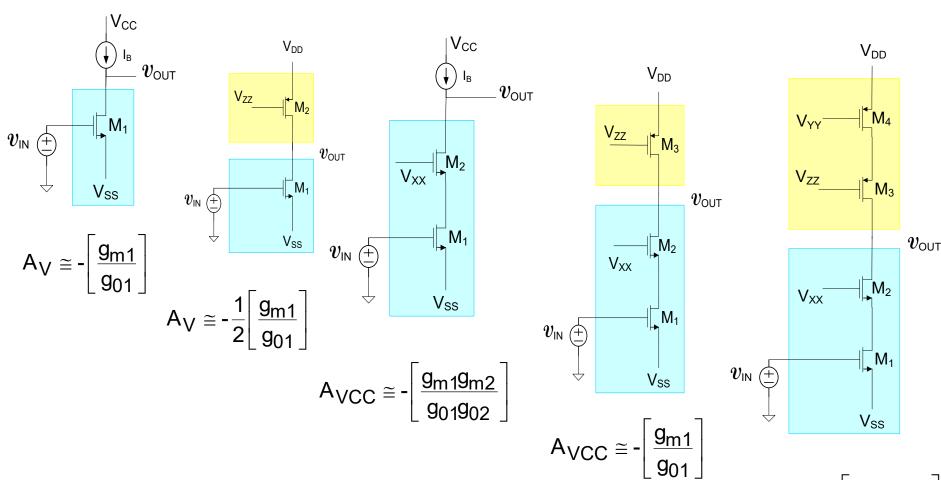

#### Basic Amplifier Application Gain Table

(not two-port models for the four structures)

Can use these equations only when small signal circuit is EXACTLY like that shown !!

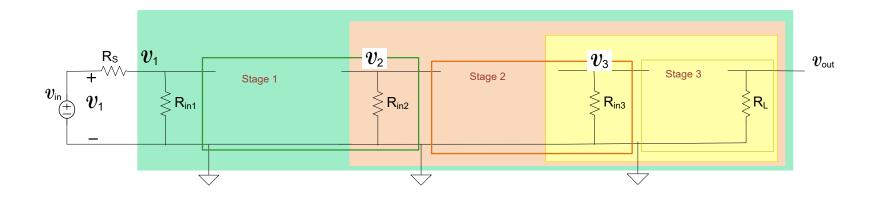

## Formalization of cascade circuit analysis working from load to input: (when stages are unilateral or not unilateral)

R<sub>ink</sub> includes effects of all loading Must recalculate if any change in loading Analysis systematic and rather simple

$$\frac{\boldsymbol{v}_{\text{OUT}}}{\boldsymbol{v}_{\text{IN}}} = \frac{\boldsymbol{v}_{\text{1}}}{\boldsymbol{v}_{\text{IN}}} \frac{\boldsymbol{v}_{\text{2}}}{\boldsymbol{v}_{\text{1}}} \frac{\boldsymbol{v}_{\text{3}}}{\boldsymbol{v}_{\text{2}}} \frac{\boldsymbol{v}_{\text{OUT}}}{\boldsymbol{v}_{\text{3}}}$$

This was the approach used in analyzing the previous cascaded amplifier

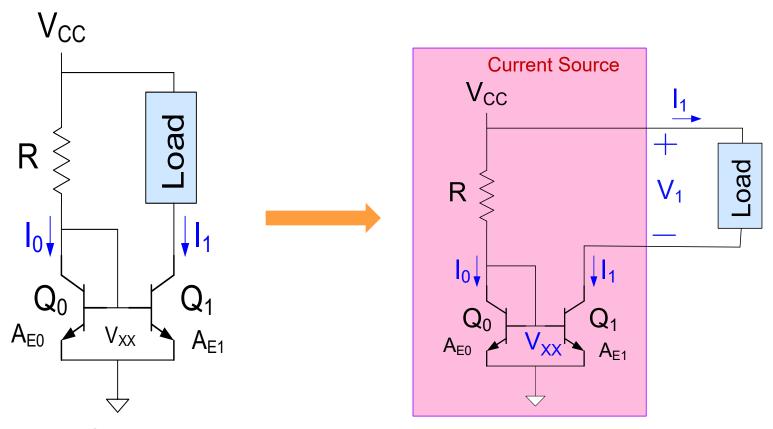

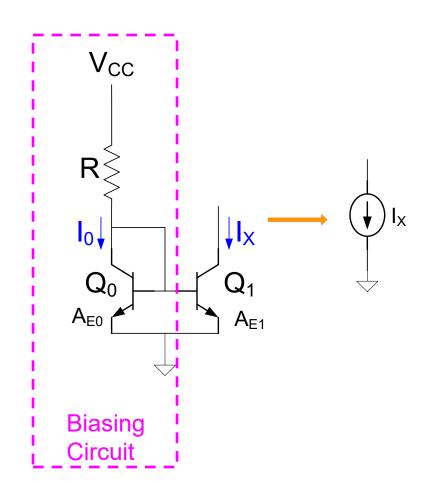

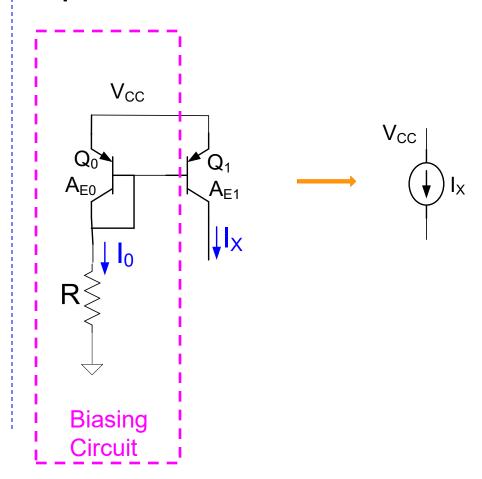

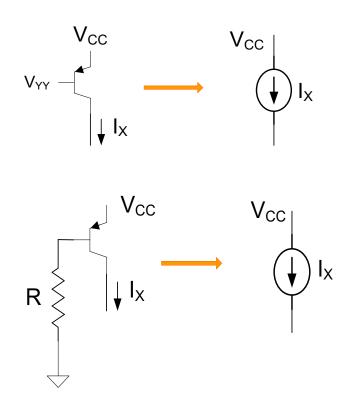

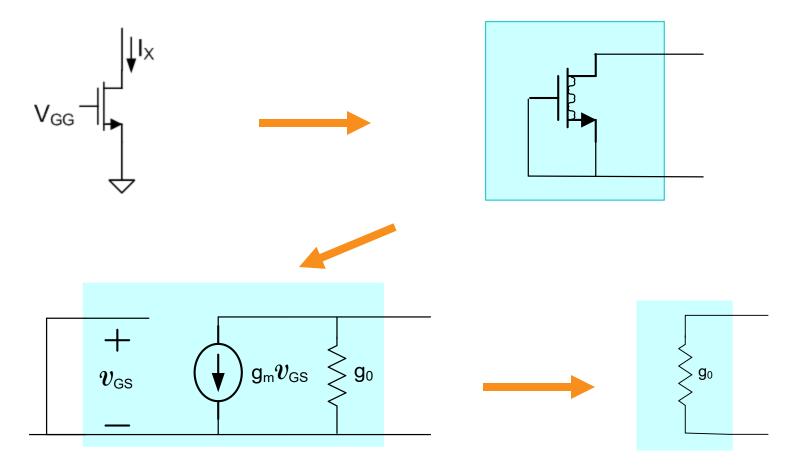

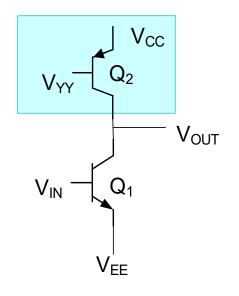

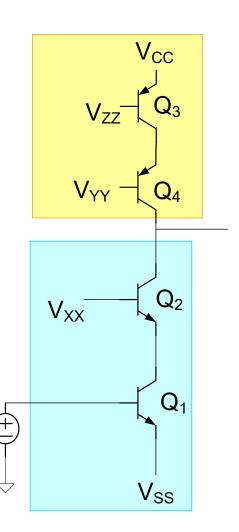

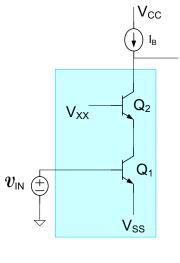

Will show circuit in red behaves as a current source

R and  $Q_0$  simply generate voltage  $V_{XX}$  in previous circuit

But sensitivity of  $I_1$  is much smaller than using voltage source for generating  $V_{\chi\chi}$

## Summary of Missing Material from Lecture 33

Start Here:

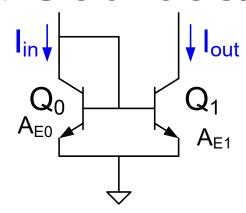

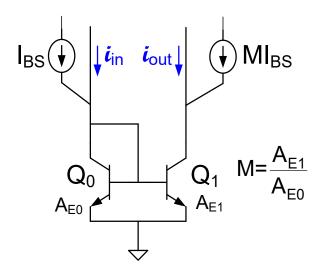

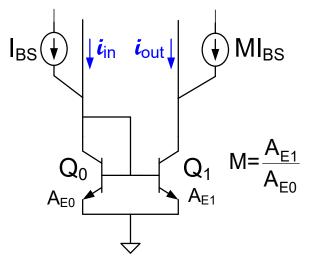

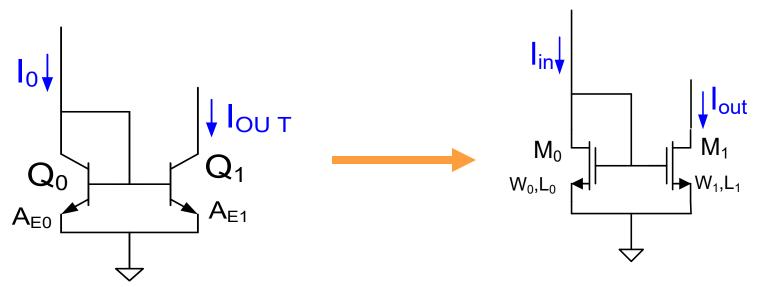

#### npn Current Mirror

If the base currents are neglected

$$I_{\text{out}} = \left[ \frac{A_{\text{E1}}}{A_{\text{E0}}} \right] I_{\text{in}}$$

- Output current linearly dependent on lin

- Small-signal and large-signal relationships the same since linear

- Serves as a current amplifier

- Widely used circuit

But I<sub>in</sub> must be positive!

npn current mirror amplifier

$$\frac{i_{\text{OUT}} + \text{MI}_{\text{BS}}}{i_{\text{in}} + \text{I}_{\text{BS}}} = \text{M}$$

$$i_{\text{OUT}} + \text{MI}_{\text{BS}} = \text{M} \left( i_{\text{in}} + \text{I}_{\text{BS}} \right)$$

$$i_{\text{OUT}} + \text{MI}_{\text{BS}} = \text{M} \left( i_{\text{in}} + \text{I}_{\text{BS}} \right)$$

$$\frac{i_{\text{OUT}}}{i_{\text{in}}} = \text{M}$$

$$i_{\text{in}}$$

But  $I_{\text{BS}} + i_{\text{in}} > 0$ !

npn current mirror amplifier

$$i_{\text{out}} = \left[\frac{A_{\text{E1}}}{A_{\text{E0}}}\right] i_{\text{in}}$$

Amplifies both positive and negative currents (provided i<sub>IN</sub>>-I<sub>BS</sub>)

Current amplifiers are easy to build !!

Current gain can be accurately controlled with appropriate layout !!

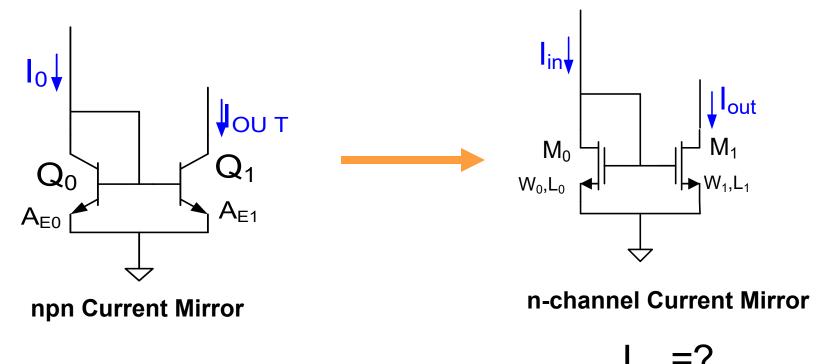

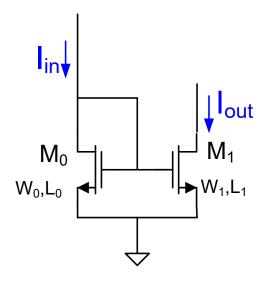

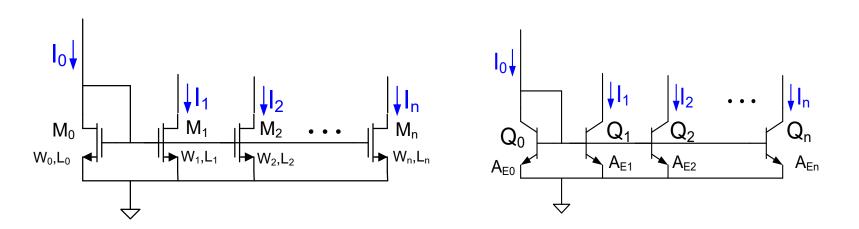

#### n-channel Current Mirror

$$I_{in} = \frac{\mu C_{OX} W_0}{2L_0} (V_{GS0} - V_{T0})^2$$

$$I_{out} = \frac{\mu C_{OX} W_1}{2L_1} (V_{GS1} - V_{T1})^2$$

If process parameters are matched, it follows that

$$\mathbf{I}_{\text{out}} = \left[ \frac{\mathbf{W}_1}{\mathbf{W}_0} \frac{\mathbf{L}_0}{\mathbf{L}_1} \right] \mathbf{I}_{\text{in}}$$

- Current mirror gain <u>can</u> be accurately controlled!

- Layout is important to get accurate gain (for both MOS and BJT)

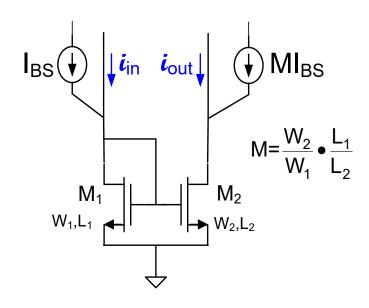

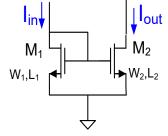

#### n-channel current mirror current amplifier

$$i_{\text{out}} = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right] i_{\text{in}}$$

Amplifies both positive and negative currents

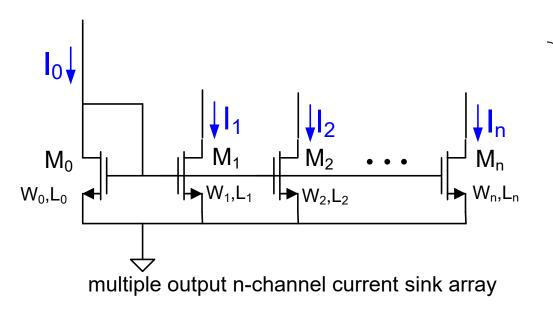

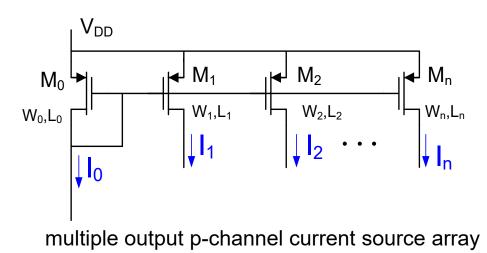

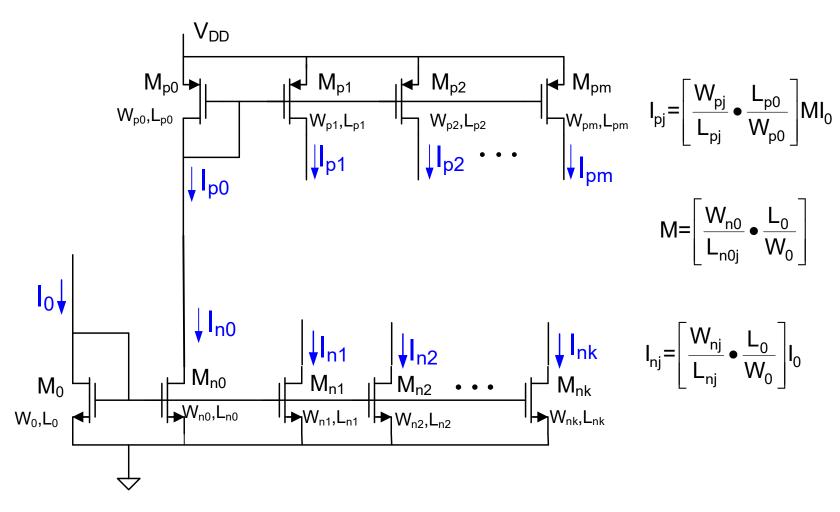

$$I_{k} = \left[\frac{W_{k}}{W_{0}} \frac{L_{0}}{L_{k}}\right] I_{0}$$

multiple sourcing and sinking current outputs

m and k may be different Often M=1

## Current Sources/Mirrors Summary

npn Current Mirror

$$I_{\text{out}} = \left[ \frac{A_{\text{E1}}}{A_{\text{E0}}} \right] I_{\text{in}}$$

n-channel Current Mirror

$$\mathbf{I}_{\text{out}} = \left[ \frac{\mathbf{W}_1}{\mathbf{W}_0} \frac{\mathbf{L}_0}{\mathbf{L}_1} \right] \mathbf{I}_{\text{in}}$$

- Current mirror gain <u>can</u> be accurately controlled!

- Layout is important to get accurate gain (for both MOS and BJT)

## Summary of Missing Material from Lecture 33

**End Here:**

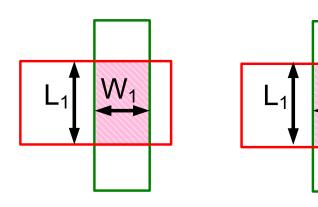

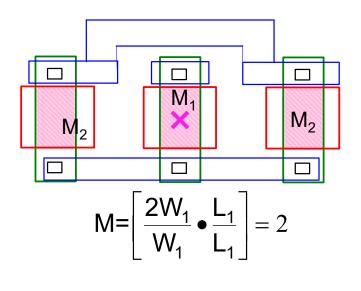

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

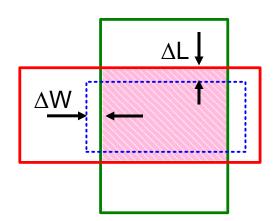

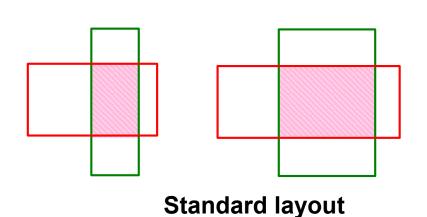

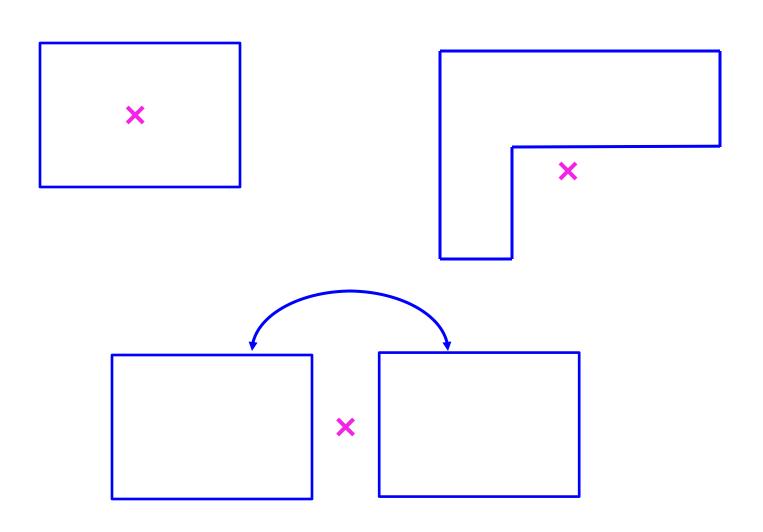

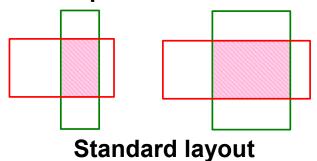

#### **Standard layout**

$W_2$

$$M = \left[ \frac{W_2 + 2\Delta W}{W_1 + 2\Delta W} \bullet \frac{L_1 + 2\Delta L}{L_2 + 2\Delta L} \right]$$

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 2\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] \neq 2$$

Gate area after fabrication depicted

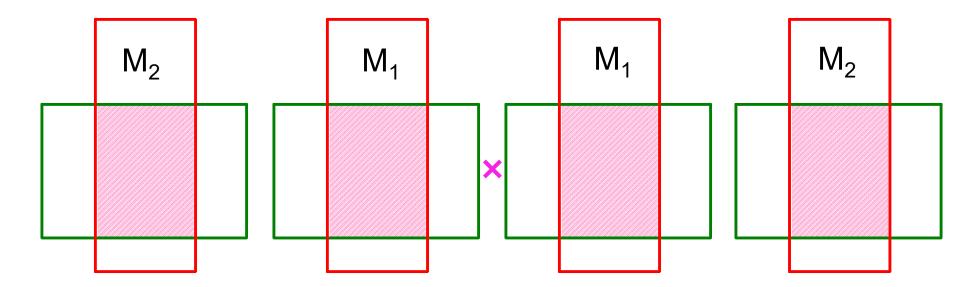

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

$$M = \left[ \frac{2W_1 + 2\Delta W}{W_1 + 2\Delta W} \bullet \frac{L_1 + 2\Delta L}{L_1 + 2\Delta L} \right] \neq 2$$

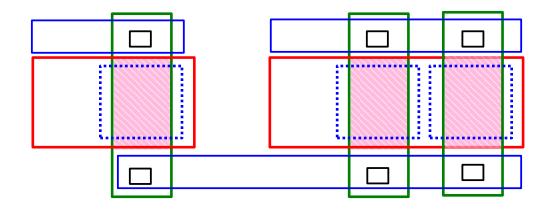

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] = 2$$

#### **Better Layout**

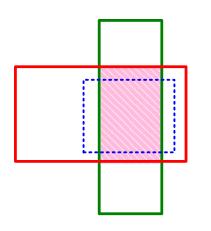

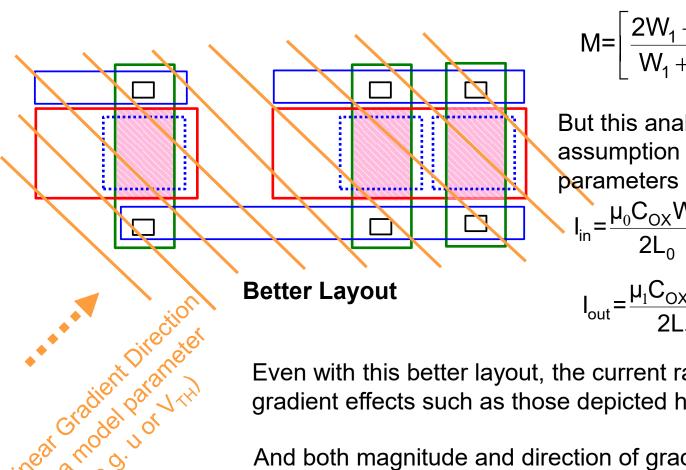

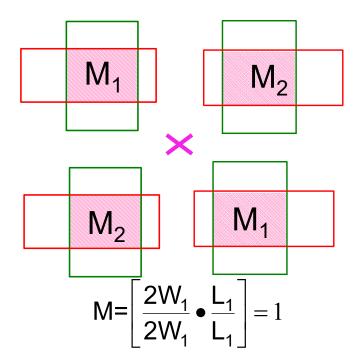

#### Example with M = 2

$$\mathsf{M} = \left\lceil \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right\rceil = 2$$

But this analysis was based upon assumption of matching of process

$$I_{in} = \frac{\mu_0 C_{OX} W_0}{2L_0} (V_{GS0} - V_{T0})^2$$

$$I_{out} = \frac{\mu_1 C_{OX} W_1}{2L_1} (V_{GS1} - V_{T1})^2$$

Even with this better layout, the current ratio will not be 2 if gradient effects such as those depicted here are shown

And both magnitude and direction of gradient effects are a random variable which will vary across a die

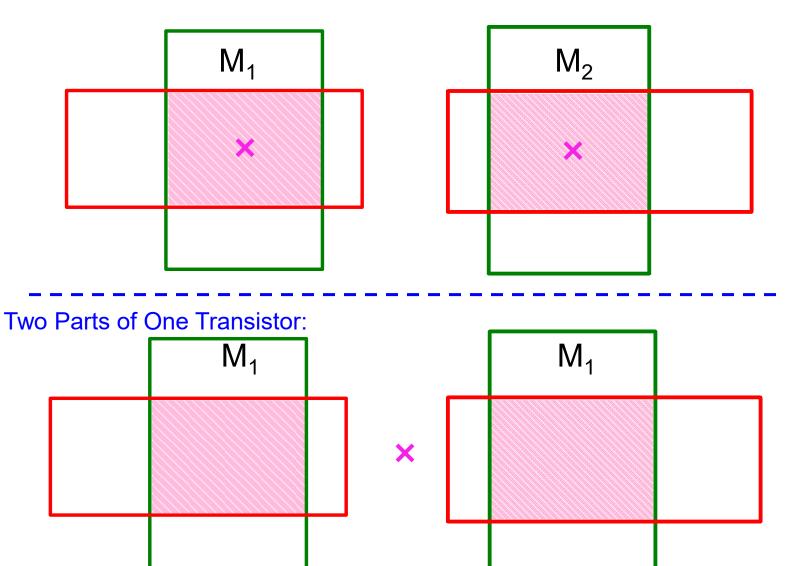

X Denotes Geometric Centroid

Geometric Centroids of Channel

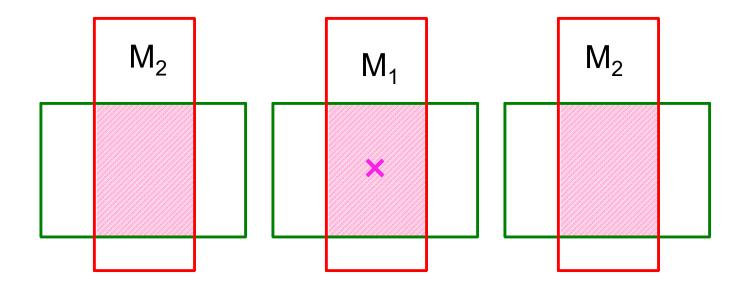

#### Two Transistors:

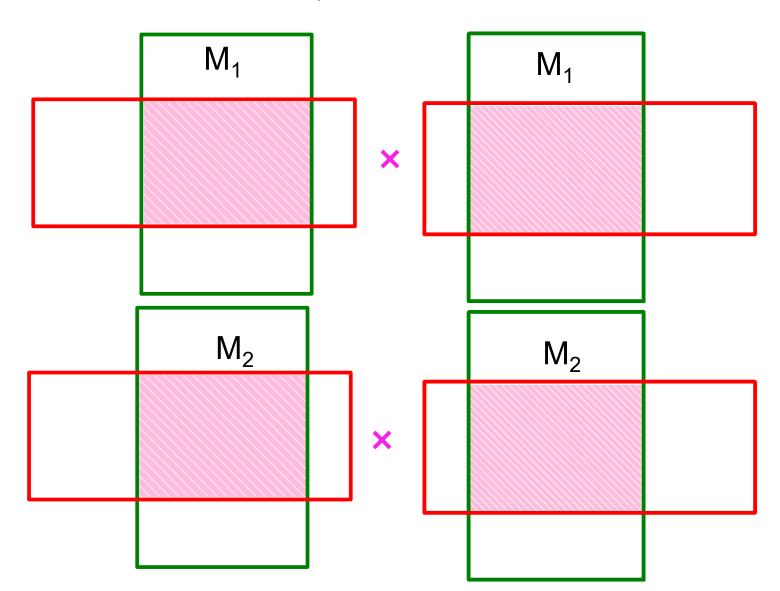

Two Transistors each with two parts:

Common Centroid for Ideally Matched Devices

Two Transistors each with two parts:

Common Centroid for Matched Devices

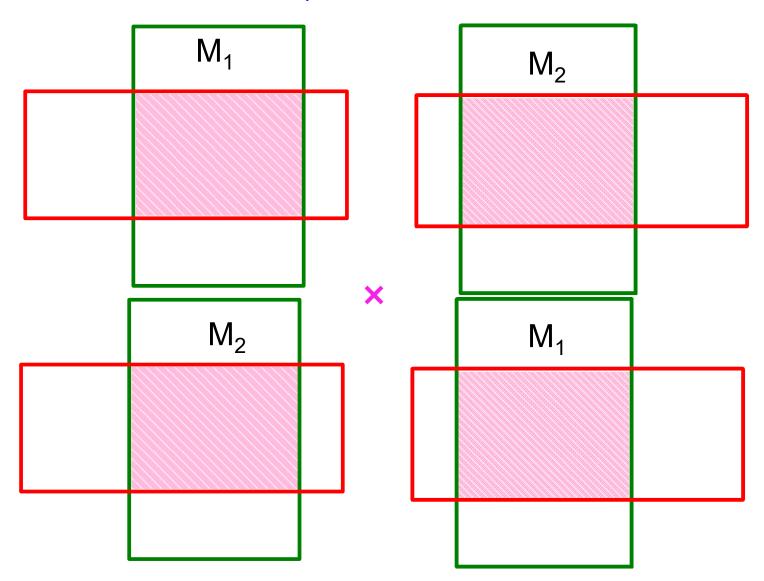

Two Transistors each with two parts:

Common Centroid for Ratioed Devices

$$M = \frac{W_2}{W_1} \frac{L_1}{L_2} = 2$$

Two Transistors with different effective widths:

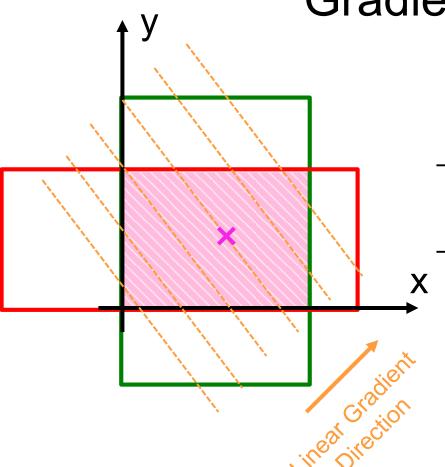

## Gradient

Threshold voltage dependent upon position

$$V_{TH}(x,y)$$

- Significant changes in threshold voltage can occur due to gradient effects

- This can seriously degrade matching in matching-critical circuits

- If the threshold voltage of a transistor changes with position, it can be reasonably accurately modeled with an "equivalent" threshold voltage

- For linear gradient, V<sub>THEQ</sub>=V<sub>TH</sub>(X<sub>C</sub>,Y<sub>C</sub>)

$$\mathbf{X}:(\mathbf{X}_{\mathbf{C}},\mathbf{Y}_{\mathbf{C}})$$

#### Example with M = 2

$$M = \left[ \frac{W_2}{W_1} \frac{L_1}{L_2} \right]$$

$$\mathsf{M} = \left\lceil \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right\rceil = 2$$

**Even Better Layout**

$$\mathsf{M} = \left[ \frac{2\mathsf{W}_1 + 4\Delta\mathsf{W}}{\mathsf{W}_1 + 2\Delta\mathsf{W}} \bullet \frac{\mathsf{L}_1 + 2\Delta\mathsf{L}}{\mathsf{L}_1 + 2\Delta\mathsf{L}} \right] = 2$$

- This is termed a common-centroid layout

- Linear gradient mismatch eliminated with common-centroid layout!

## Common-Centroid Layouts

- Individual transistors often decomposed into parallel multiple unary devices connected in parallel

- Common-Centroid layout approach widely used to minimize (ideally cancel) gradient effects in matching-critical circuits

- Applications extend well beyond current mirrors

- More than 2 devices can share a common centroid

If I<sub>0</sub> is practically generated (it can be), now have available a large number of accurate current sources or sinks that can be used for biasing and for other purposes on chip!

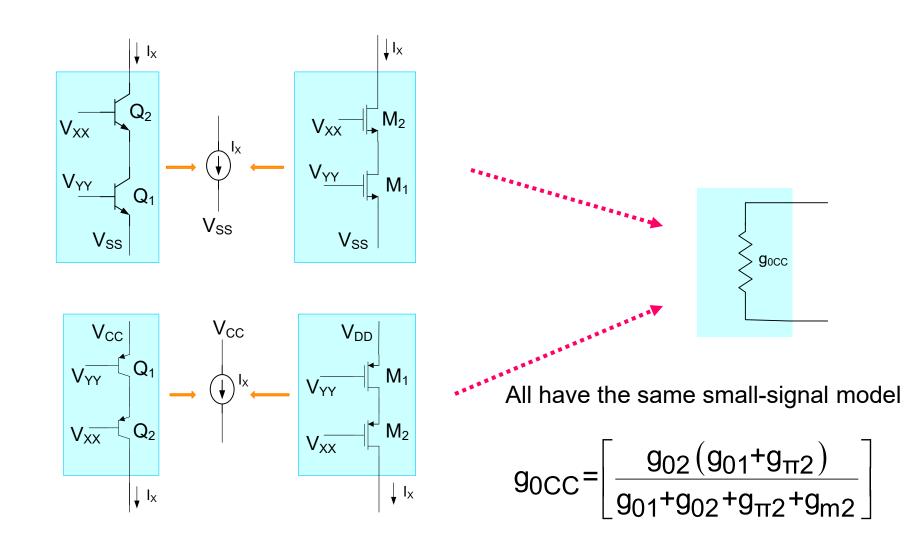

# Will now return to discussion of high gain amplifiers

#### Why are we interested in high-gain amplifiers?

- High gain amplifiers typically have some very undesirable properties

Nonlinear, gain highly dependent upon process variations and temperature, frequency response poor, noisy, ....

- So we can build feedback amplifiers !!

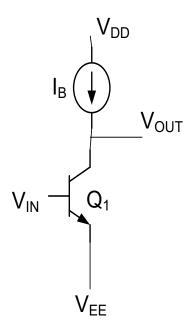

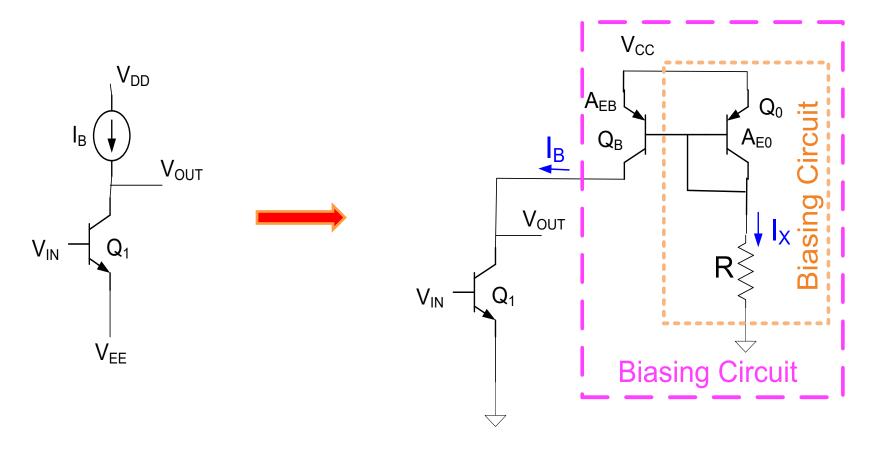

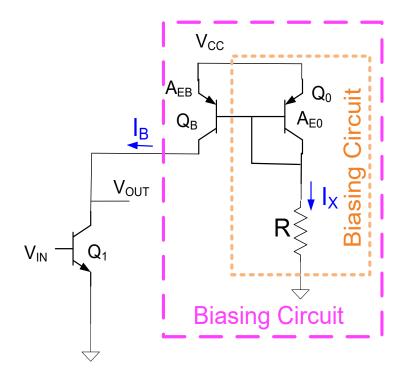

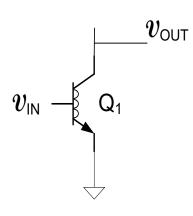

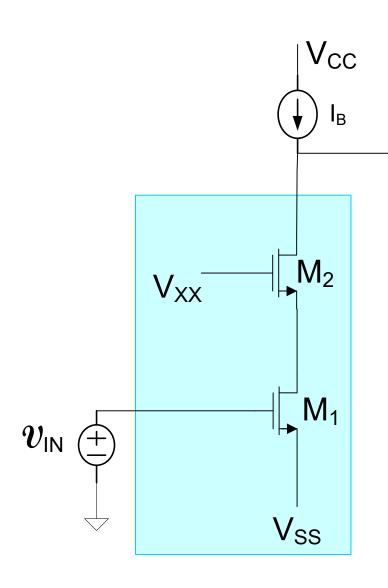

How can we build the current source?

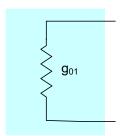

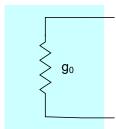

What is the small-signal model of an actual current source?

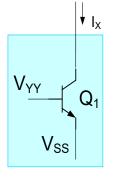

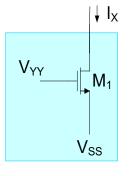

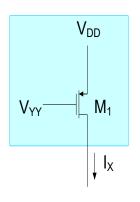

## **Basic Current Sources and Sinks**

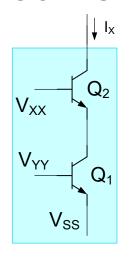

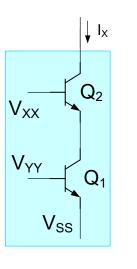

#### **Bipolar Mirror-Based Current Sink**

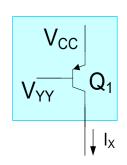

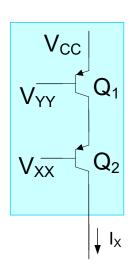

#### **Bipolar Mirror-Based Current Source**

Biasing circuit uses same V<sub>CC</sub> as amplifier and no other independent sources

- Bias circuitry requires only a single independent dc voltage source, resistor, and BJT!

- Incremental overhead is only one transistor, Q<sub>B</sub>

How can we build the current source?

→ What is the small-signal model of an actual current source?

## **Basic Current Sources and Sinks**

What is the small-signal model of an actual current source?

#### **Basic Bipolar Current Sinks**

# $V_{CC}$

**Basic Bipolar Current Sources**

- Very practical methods for biasing the BJTs (or MOSFETs) can be used

- Current Mirrors often used for generating sourcing and sinking currents

- Can think of biasing transistors with  $V_{XX}$  and  $V_{YY}$  in these current sources

### **Basic Current Sources and Sinks**

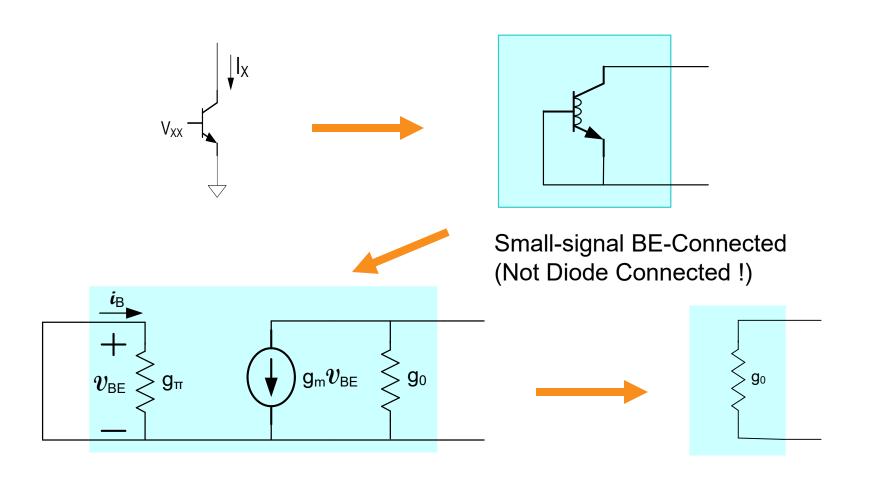

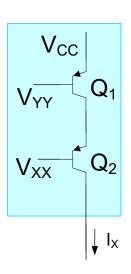

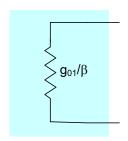

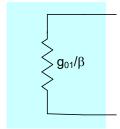

**Small-signal Model of BJT Current Sinks and Sources**

### **Basic Current Sources and Sinks**

**Small-signal Model of BJT Current Sinks and Sources**

Small-signal model of all other BJT Sinks and Sources introduced so far are the same

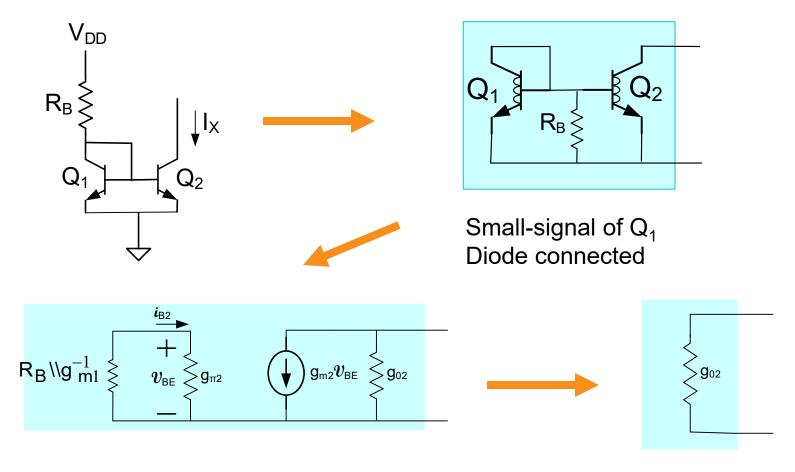

### **Basic Current Sources and Sinks**

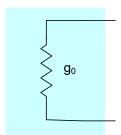

**Small-signal Model of MOS Current Sinks and Sources**

Small-signal model of all other MOS Sinks and Sources introduced thus far are the same

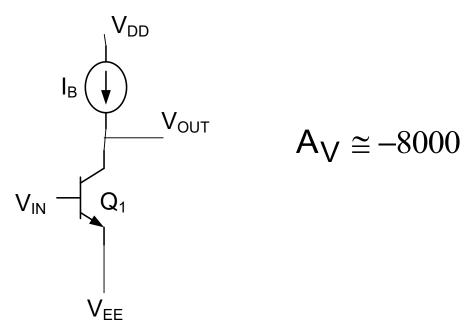

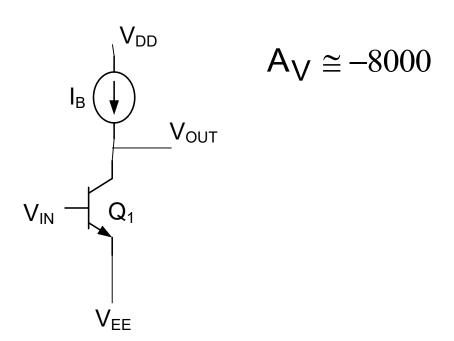

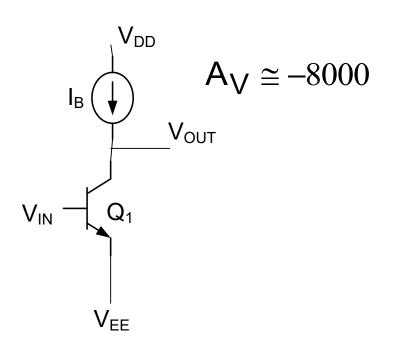

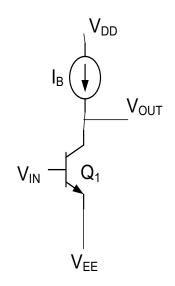

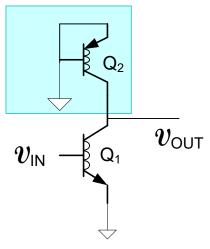

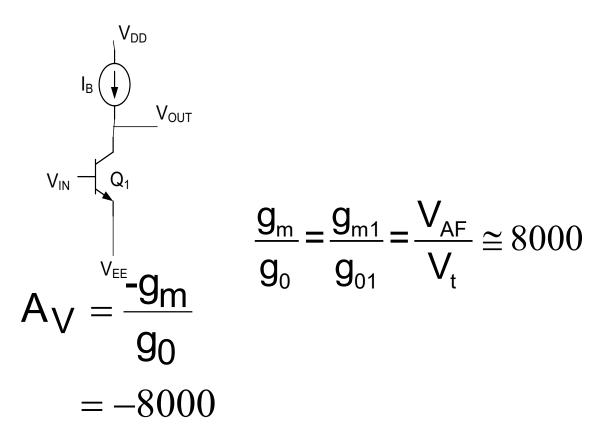

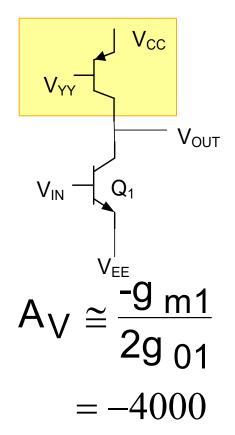

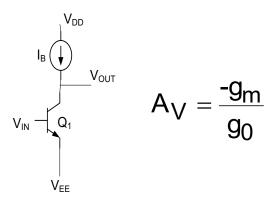

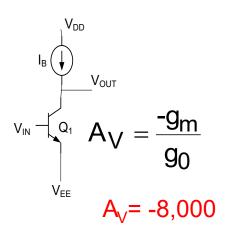

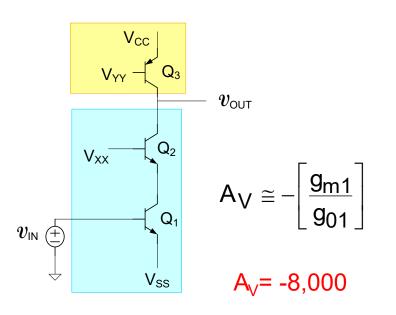

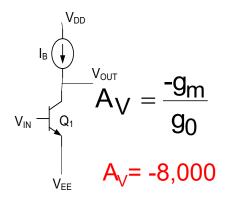

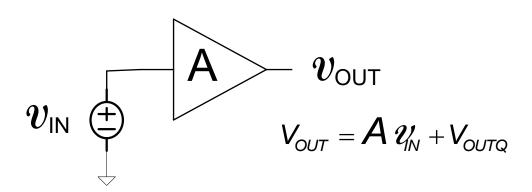

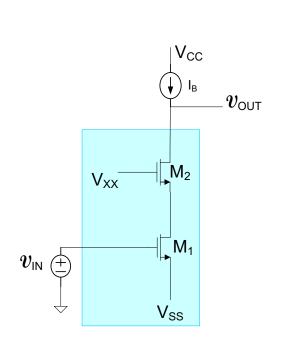

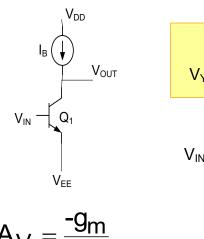

# High-gain amplifier

$$A_V = \frac{-g_m}{g_0}$$

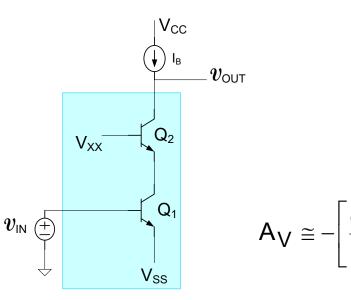

$$v_{\mathsf{IN}} + v_{\mathsf{BE1}} > \mathsf{g}_{\mathsf{m1}}$$

$v_{\mathsf{BE1}} > \mathsf{g}_{\mathsf{m1}}$   $v_{\mathsf{BE1}} > \mathsf{g}_{\mathsf{01}}$

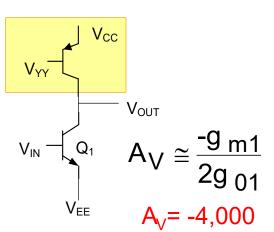

$$A_V = \frac{-9m1}{901 + 902} \cong \frac{-9m1}{2901}$$

# High-gain amplifier

- Nonideal current source decreased the gain by a factor of 2

- But the voltage gain is still quite large (-4000)

Can the gain be made even larger?

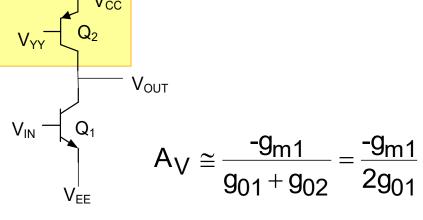

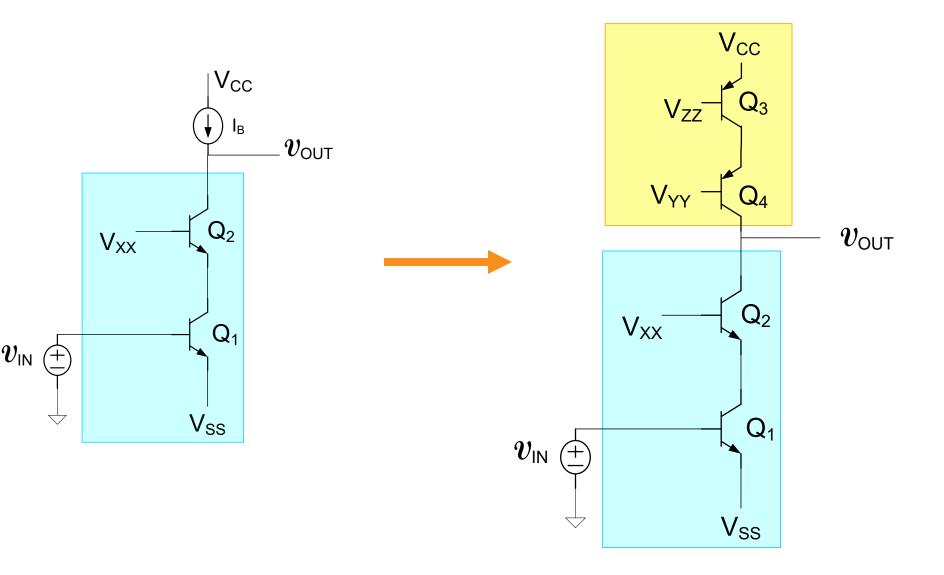

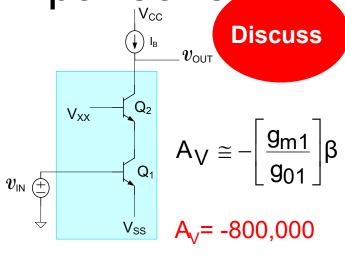

# High-gain amplifier

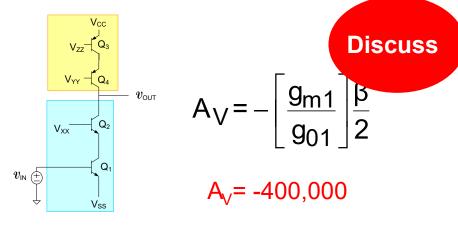

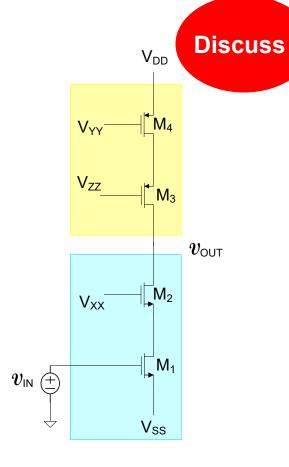

Discuss

Can the gain be made even larger?

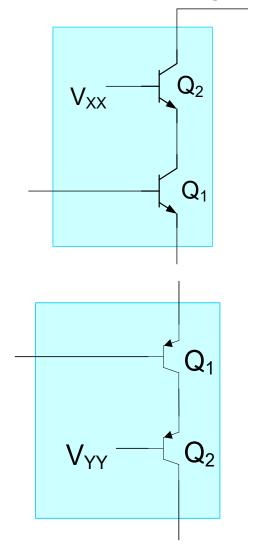

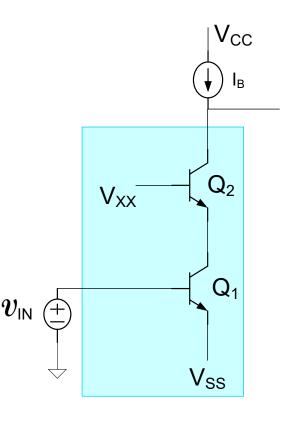

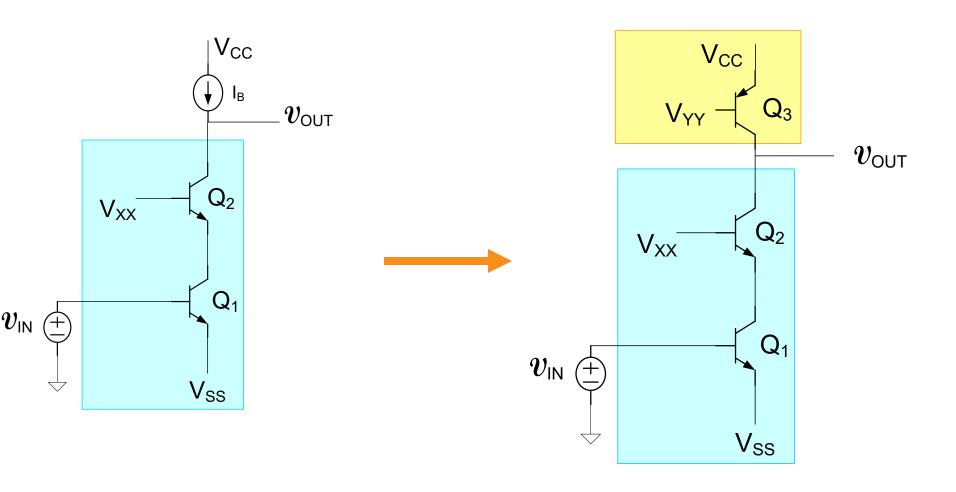

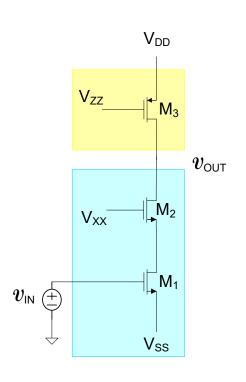

#### **The Cascode Configuration**

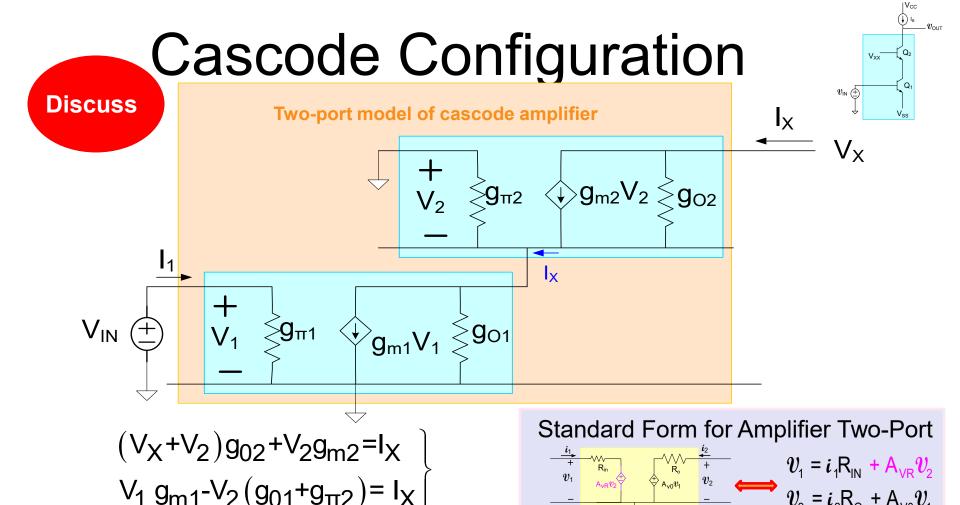

#### The Cascode Amplifier (consider npn BJT version)

- Actually a cascade of a CE stage followed by a CB stage but usually viewed as a "single-stage" structure

- Cascode structure is widely used

#### **Basic Amplifier Structures**

- 1. Common Emitter/Common Source

- 2. Common Collector/Common Drain

- 3. Common Base/Common Gate

- 4. Common Emitter with R<sub>F</sub>/ Common Source with R<sub>S</sub>

- 5. Cascode (actually CE:CB or CS:CD cascade)

- 6. Darlington (special CE:CE or CS:CS cascade)

The first 4 are most popular

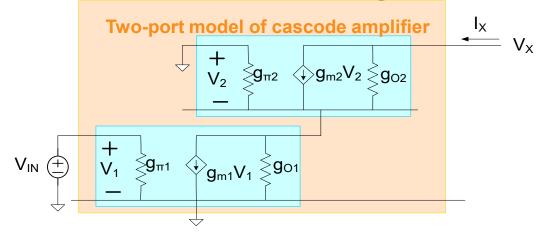

### The Cascode Amplifier (consider npn BJT version) $_{ extsf{-}}v_{ extsf{out}}$ $Q_2$ $V_{\text{SS}}$ I<sub>X</sub> $Q_2$ $\diamondsuit g_{m2}V_2 \lessapprox g_{O2}$ $\leq g_{\pi 2}$ $Q_1$ + V<sub>1</sub> $g_{\pi 1}$

Observing V<sub>1</sub>=V<sub>IN</sub> and eliminating V<sub>2</sub> between these two equations, we obtain

$$V_{IN} = I_{1} \bullet \frac{1}{g_{\pi 1}}$$

and

$$V_{X} = I_{X} \bullet \left[ \frac{g_{01} + g_{02} + g_{\pi 2} + g_{m2}}{g_{02}(g_{01} + g_{\pi 2})} \right] - V_{IN} \bullet \left[ \frac{g_{m1}(g_{02} + g_{m2})}{g_{02}(g_{\pi 2} + g_{01})} \right]$$

$$V_{X} = I_{X} \bullet \left[ \frac{g_{01} + g_{02} + g_{\pi 2} + g_{m2}}{g_{02} (g_{01} + g_{\pi 2})} \right] - V_{IN} \bullet \left[ \frac{g_{m1} (g_{02} + g_{m2})}{g_{02} (g_{\pi 2} + g_{01})} \right]$$

$$V_{IN} = I_1 \bullet \frac{1}{g_{\pi 1}}$$

#### It thus follows for the npn bipolar structure that :

$$A_{VCC} = -\left[\frac{g_{m1}(g_{02} + g_{m2})}{g_{02}(g_{\pi 2} + g_{01})}\right] = -\left[\frac{g_{m1}g_{m2}}{g_{02}g_{\pi 2}}\right]$$

$$g_{0CC} = \left[ \frac{g_{02} \left( g_{01} + g_{\pi 2} \right)}{g_{01} + g_{02} + g_{\pi 2} + g_{m2}} \right] \cong \left[ \frac{g_{02} g_{\pi 2}}{g_{m2}} \right]$$

$$A_{VCC} \cong - \left[ \frac{g_{m1}g_{m2}}{g_{02}g_{\pi2}} \right]$$

$$g_{0CC} \cong \begin{bmatrix} \frac{g_{02}g_{\pi 2}}{g_{m2}} \end{bmatrix}$$

$$g_{\pi CC} = g_{\pi 1}$$

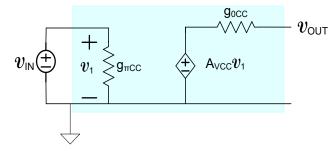

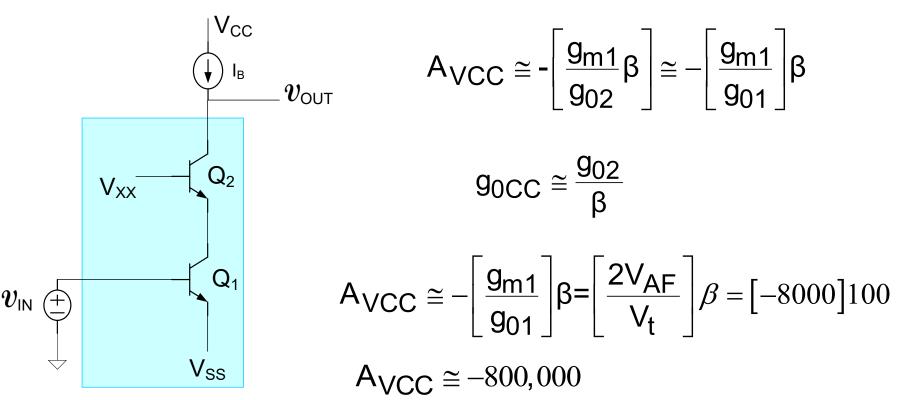

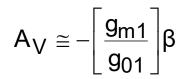

$$A_{VCC} \cong -\left[\frac{g_{m1}}{g_{02}}\beta\right] \cong -\left[\frac{g_{m1}}{g_{01}}\right]\beta$$

$$g_{0CC} \cong \frac{g_{01}}{\beta}$$

- Voltage gain is a factor of β larger than that of the CE amplifier with current source load

- Output impedance is a factor of β larger than that of the CE amplifier

This gain is very large and only requires two transistors!

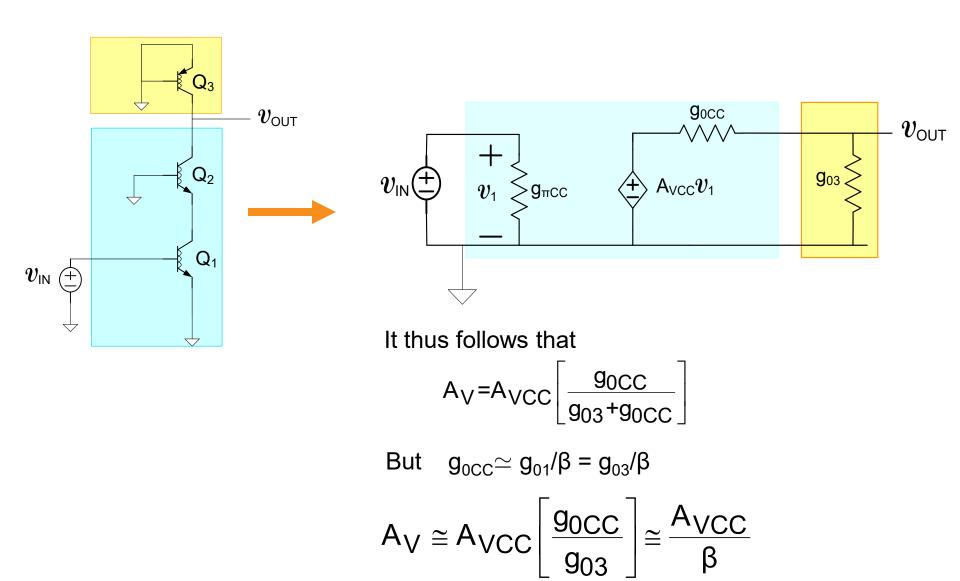

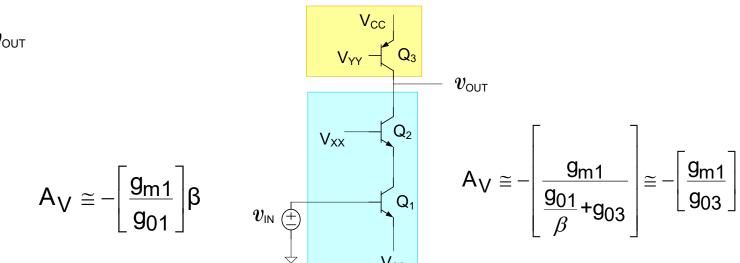

What happens to the gain if a transistor-level current source is used for  $I_R$ ?

### High-gain amplifier comparisons

This is a dramatic reduction in gain compared to what the ideal current source biasing provided

$$A_{V} \cong A_{VCC} \left[ \frac{g_{0CC}}{g_{03}} \right] \cong \frac{A_{VCC}}{\beta}$$

**But recall**

$$A_{VCC} \cong - \left| \frac{g_{m1}}{g_{01}} \right| \beta$$

**Thus**

$$A_{V} \cong -\left[\frac{g_{m1}}{g_{01}}\right]$$

$$A_{V} \cong - \begin{vmatrix} I_{CQ} / V_{t} \\ I_{CQ} / V_{AF} \end{vmatrix} = - \left[ \frac{V_{AF}}{V_{t}} \right] \cong -8000$$

- This is still a factor of 2 better than that of the CE amplifier with transistor current source  $A_{VCE} = -\left[\frac{g_{m1}}{2g_{01}}\right]$

- It only requires one additional transistor

- But its not nearly as good as the gain the cascode circuit seemed to provide

### Cascode Configuration Comparisons

Gain limited by output impedance of current scource !!

Can we design a better current source?

In particular, one with a higher output impedance?

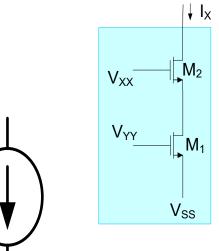

### Better current sources

Need a higher output impedance than go

$$g_{0CC} \cong \frac{g_{01}}{\beta}$$

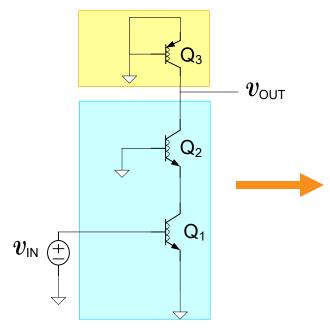

Can a current source be built with the cascode circuit?

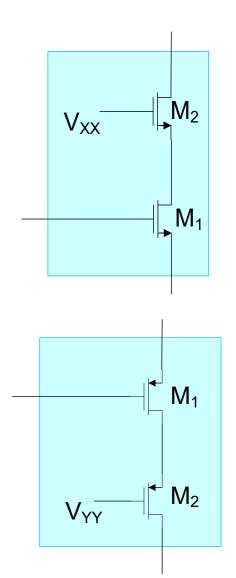

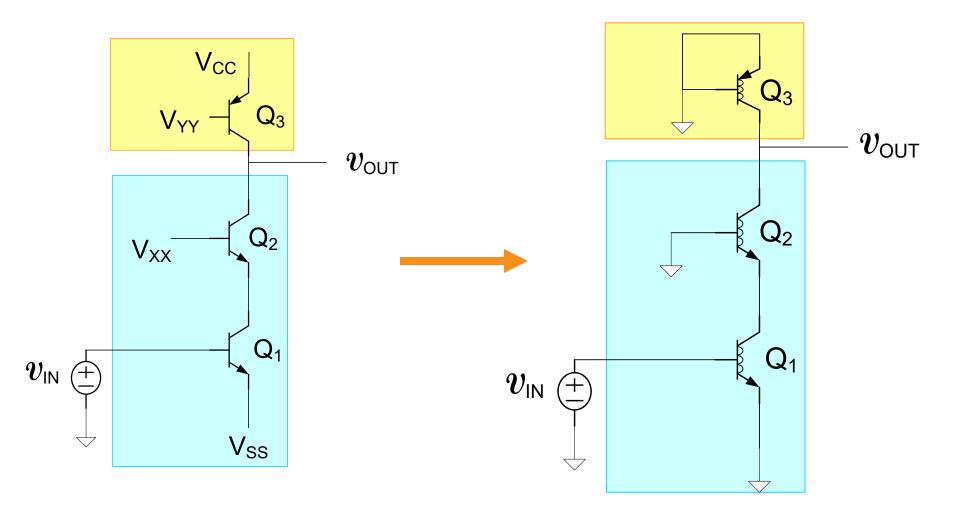

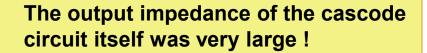

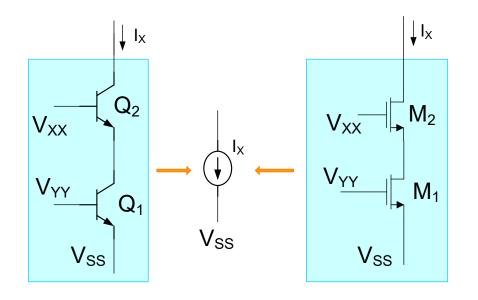

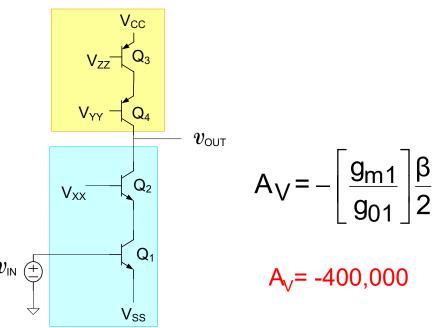

#### Cascode current sources

#### Cascode current sources

#### Cascode current sources

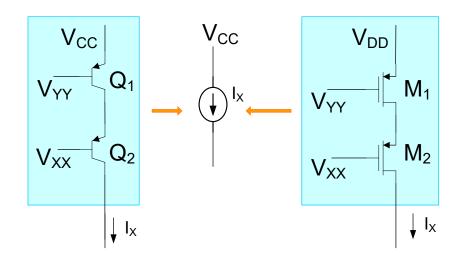

#### For the BJT cascode current sources

$$g_{0CC} = \left[ \frac{g_{02} (g_{01} + g_{\pi 2})}{g_{01} + g_{02} + g_{\pi 2} + g_{m2}} \right] \approx \left[ \frac{g_{02} g_{\pi 2}}{g_{m2}} \right] = \frac{g_{01}}{\beta}$$

$v_{\mathsf{IN}}$

$v_{\mathsf{out}}$

$$A_{V} \cong -\left[\frac{g_{m1}}{\frac{g_{01}}{\beta_{1}} + g_{0CC}}\right] \cong -\left[\frac{g_{m1}}{\frac{g_{01}}{\beta_{1}} + \frac{g_{03}}{\beta_{3}}}\right]$$

$$A_{V} = - \left[ \frac{g_{m1}}{g_{01}} \right] \frac{\beta}{2}$$

If  $\beta_1 = \beta_3 = \beta$

$$A_V = -[8000] \frac{100}{2} \cong -400,000$$

- This gain is very large and is a factor of 2 below that obtained with an ideal current source biasing

- Although the factor of 2 is not desired, the performance of this circuit is still very good

- This factor of 2 gain reduction is that same as was observed for the CE amplifier when a transistor-level current source was used

- Biasing voltages V<sub>ZZ</sub> and V<sub>SS</sub> are critical so seldom used single-ended but good biasing strategies exist for differential operation

Cascode Configuration Comparisons

Can we use more cascoding to further increase the gain?

### High Gain Amplifiers Seldom Used Open Loop

If  $A_V$ =-400,000 and  $V_{IN}$  increases by 1mV, what would happen at the output?

$|V_{OUT}|$  would increase by 400,000 x 1mV=-400V

#### The Cascode Amplifier (consider n-ch MOS version)

**Discuss**

$$A_{VCC} \cong - \left[ \frac{g_{m1}g_{m2}}{g_{01}g_{02}} \right]$$

$$g_{0CC} \cong \left[ \frac{g_{01}g_{02}}{g_{m2}} \right]$$

Same issues for biasing with current source as for BJT case

With cascode current source for  $I_B$ , gain only drops by a factor of 2 from value with ideal current source

#### The Cascode Amplifier (consider n-ch MOS version)

$$A_{VCC} \cong - \left[ \frac{g_{m1}g_{m2}}{g_{01}g_{02}} \right]$$

$$A_{VCC} \cong -\left[\frac{g_{m1}}{g_{01}}\right]$$

$$A_{VCC} \cong -\left[\frac{g_{m1}}{g_{01}}\right]$$

$A_{VCC} \cong -\frac{1}{2}\left[\frac{g_{m1}g_{m2}}{g_{01}g_{02}}\right]$

### Current Source Summary (BJT)

#### **Basic**

$$g_0 \cong g_{01}$$

#### **Cascode**

$$g_{0CC} \cong \frac{g_{01}}{\beta}$$

### Current Source Summary (MOS)

#### **Basic**

$$g_0 \cong g_{01}$$

#### **Cascode**

$$g_0\cong g_{01}\frac{g_{02}}{g_{m2}}$$

#### High Gain Amplifier Comparisons (n-ch MOS)

$$A_{VCC} \cong -\frac{1}{2} \left[ \frac{g_{m1}g_{m2}}{g_{01}g_{02}} \right]$$

### High Gain Amplifier Comparisons (BJT)

Single-ended high-gain amplifiers inherently difficult to bias (because of the high gain)

$V_{OUT}$

- Biasing becomes practical when used in differential applications

- These structures are widely used but usually with differential inputs

$$A_{V} = -\left[\frac{g_{m1}}{g_{01}}\right] \frac{\beta}{2}$$

Stay Safe and Stay Healthy!

### End of Lecture 34